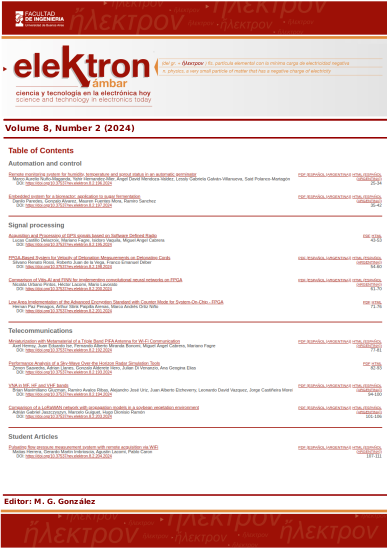

Low Area Implementation of the Advanced Encryption Standard with Counter Mode for System-On-Chip - FPGA

DOI:

https://doi.org/10.37537/rev.elektron.8.2.201.2024Keywords:

advanced encryption standard (AES), counter mode (CTR), field programable gate array (FPGA), System on Chip (SoC), Zynq7000, XilinxAbstract

Cryptography plays a crucial role in protecting information on public networks. The implementation of AES with CTR on Xilinx SoC-FPGA devices, such as Zynq 7000 and Kintex 7, aims to enhance security in IoT devices and embedded systems. The goal is to ensure data confidentiality and availability in connected environments, prioritizing low area usage, low power consumption, and high performance. Implementation was made using a Very High-Speed Integrated Circuit Hardware Description Language (VHDL) on Vivado 2019-2. The results show its area utilization for AES and AES-CTR implementations, with a throughput of 1.8 and 7.67 Gbps for Zynq 7000 and, 2.72 and 11.11 Gbps for Kintex 7; they are also presented for a 128-bits key size and four CTR blocks. VHDL generics can be configured to be 192-bit and 256-bit lengths with different block sizes. Implemented AES-CTR IP showed correct behavior for 128, 192, and 256 key sizes with four CTR blocks. A cipher process with sizes 192 and 256 requires additional cycles that affect the timing performance and hardware utilization.Downloads

References

J. K. Cheng, E. M. Lim, Y. Y. Krikorian, D. J. Sklar, and V. J. Kong, "A Survey of Encryption Standard and Potential Impact Due to Quantum Computing," The Aerospace Corporation, vol. 1, no. 1, pp. 1-10, 2023.

M. Althoff et al., "CRC-Oriented Error Detection Architectures of Post-Quantum Cryptography Niederreiter Key Generator on FPGA," Proceedings of the International Conference on Field-Programmable Technology (ICFPT), 2022.

P. Werner et al., "Error Detection Schemes Assessed on FPGA for Multipliers in Lattice-Based Key Encapsulation Mechanisms in Post-Quantum Cryptography," IEEE Transactions on Computers, vol. 71, no. 4, pp. 751-764, 2022.

L. Chen, W. Ye, J. He, and X. Ma, "Vulnerability Assessment of Blockchain Using Confrontation Deduction," School of Electronics and Information Engineering, Tongji University, vol. 1, no. 1, pp. 1-10, 2023.

Y. Shen et al., "Lightweight Hardware Architectures for Fault Diagnosis Schemes of Efficiently-Maskable Cryptographic Substitution Boxes," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 69, no. 10, pp. 4203-4212, 2022.

S. Gajbhiye, S. Karmakar, M. Sharma, and S. Sharma, "Paradigm Shift from Classical Cryptography to Quantum Cryptography," CSE-FET, SSGI, SSTC, vol. 1, no. 1, pp. 1-10, 2023.

Circuits and Systems Conference (NorCAS), 2022. DOI: 10.1109/NorCAS57515.2022.9934378.

P. Sikka, A. R. Asati and C. Shekhar, "High-throughput field- programable gate array implementation of the advanced encryption standard algorithm for automotive security applications," Journal of Ambient Intelligence and Humanized Computing, 7, 2020.

E. M. Benhani, L. Bossuet and A. Aubert, "The Security of ARM TrustZone in a FPGA-Based SoC," IEEE Transactions on Computers, vol. 68, p. 1238–1248, 8 2019.

Y. Sovyn, V. Khoma, and M. Podpora, "Comparison of Three CPU-Core Families for IoT Applications in Terms of Security and Performance of AES-GCM," IEEE Internet of Things Journal, vol. 7, p. 339–348, 1 2020.

A. Silitonga, Z. Jiang, N. Khan, and J. Becker, "Reconfigurable Module of Multi-mode AES Cryptographic Algorithms for AP SoCs," in 2019 IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP and International Symposium of System-on- Chip (SoC), 2019.

I. C. Guzmán, R. D. Nieto and Á. Bernal, "FPGA implementation of the AES-128 algorithm in non-feedback modes of operation," in DYNA, vol. 83, p. 37–43, 9 2016.

P. Visconti, S. Capoccia, E. Venere, R. Velázquez and R. de Fazio, "10 Clock-Periods Pipelined Implementation of AES-128 Encryption-Decryption Algorithm up to 28 Gbit/s Real Throughput by Xilinx Zynq UltraScale+ MPSoC ZCU102 Platform," in Electronics, vol. 9, p. 1665, 10 2020.

R. Cowart, D. Coe, J. Kulick, and A. Milenković, "An Implementation and Experimental Evaluation of Hardware Accelerated Ciphers in All-Programmable SoCs," in Proceedings of the SouthEast Conference, 2017.

L. Daoud, F. Hussein, and N. Rafla, "Optimization of Advanced Encryption Standard (AES) Using Vivado High-Level Synthesis (HLS)," 2019.

S. Chen, W. Hu, and Z. Li, "High-Performance Data Encryption with AES Implementation on FPGA," in 2019 IEEE 5th Intl Conference on Big Data Security on Cloud (BigDataSecurity), IEEE Intl Conference on High Performance and Smart Computing, (HPSC) and IEEE Intl Conference on Intelligent Data and Security (IDS), 2019.

S. Chhabra and K. Lata, "Hardware-Software Co-Simulation of Obfuscated 128-Bit AES Algorithm for Image Processing Applications," in 2018 IEEE International Symposium on Smart Electronic Systems (iSES) (Formerly iNiS), 2018.

R. V. Daemen, "The Design of Rijndael: AES - The Advanced Encryption Standard.," 2002. DOI: 10.1007/978-3-662-04722-4.

H. and R. P. and W. D. Lipmaa, " CTR-Mode Encryption.," 2001.

W. Stallings, “Cryptography and Network Security: Principles and Practice,” in Pearson, 2013.

Chegg, "Consider the five block cipher modes of operation shown in Table 6.1. For each mode, consider the case when cipher text block C1 is corrupted. Which plaintext blocks, when decrypted, are corrupted?" [Online]. Available: https://www.chegg.com/homework-help/questions-and- answers/1consider-five-block-cipher-modes-operation-shown- table-61-mode-consider-case-cipher-text--q15451479. [Accessed 21 11 2023].

Course Hero, "1 Consider the five block cipher modes of operation shown in Table 6.docx," 09 20 2019. [Online]. Available: https://www.coursehero.com/file/46728624/1Consider-the-five- block-cipher-modes-of-operation-shown-in-Table-6docx/. [Accessed 21 11 2023].

NIST, FIPS197, 2001.

NIST, SP-800-38A, 2001.

Xilinx, "Vivado Timing - Where can I find the Fmax in the timing report?" 2019.

Lightweight hardware architectures for fault diagnosis schemes of efficiently maskable cryptographic substitution boxes, 2016 IEEE International Conference on Electronics, Circuits and Systems, 2016. DOI: 10.1109/ICECS.2016.7841314.

CRC-oriented error detection architectures of post-quantum cryptography Niederreiter key generator on FPGA, 2022 IEEE Nordic Circuits and Systems Conference (NorCAS), 2022. DOI: 10.1109/NorCAS57515.2022.9934378.

Error Detection Schemes Assessed in FPGA for Multipliers in Lattice-Based Key Encapsulation Mechanisms in Post-quantum cryptography, IEEE Transactions on Emerging Topics in Computing, 2022. DOI: 10.1109/TETC.2022.3217.

Published

Issue

Section

License

The authors who publish in this journal agree with terms established in the license Attribution-NonCommercial-NoDerivatives 4.0 International (CC BY-NC-ND 4.0)